### **LMC835 Digital Controlled Graphic Equalizer**

### **General Description**

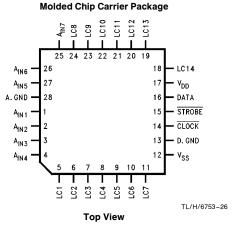

The LMC835 is a monolithic, digitally-controlled graphic equalizer CMOS LSI for Hi-Fi audio. The LMC835 consists of a Logic section and a Signal Path section made of analog switches and thin-film silicon-chromium resistor networks. The LMC835 is used with external resonator circuits to make a stereo equalizer with seven bands,  $\pm\,12$  dB or  $\pm\,6$ dB gain range and 25 steps each. Only three digital inputs are needed to control the equalization. The LMC835 makes it easy to build a  $\mu P$ -controlled equalizer.

The signal path is designed for very low noise and distortion, resulting in very high performance, compatible with

### **Features**

- No volume controls required

- Three-wire interface

- 14 bands, 25 steps each

- $\blacksquare$   $\pm$ 12 dB or  $\pm$ 6 dB gain ranges

- Low noise and distortion

- TTL, CMOS logic compatible

### **Applications**

- Hi-Fi equalizer

- Receiver ■ Car stereo

- Musical instrument

- Tape equalization

- Mixer

- Volume controller

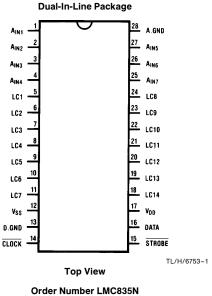

### **Connection Diagrams**

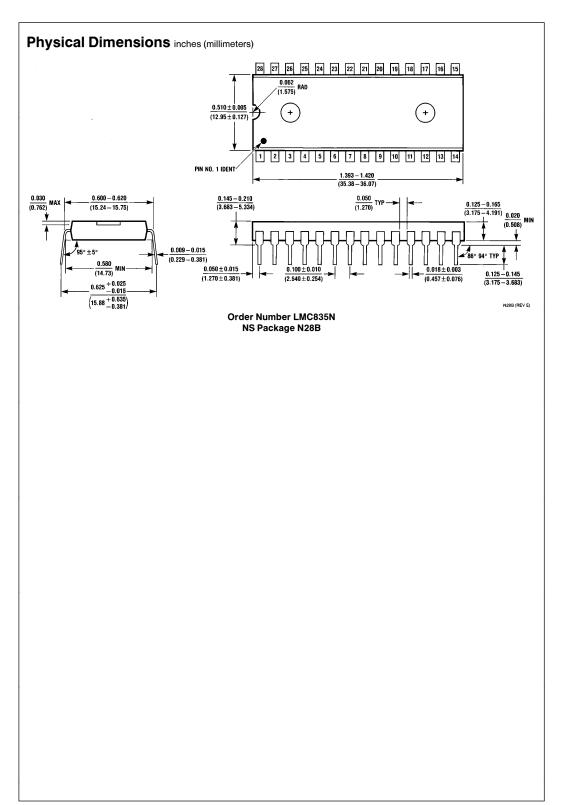

See NS Package N28B

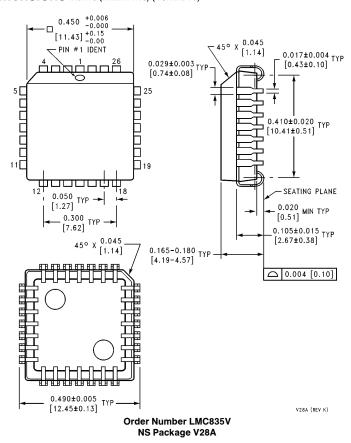

Order Number LMC835V See NS Package V28A

© 1995 National Semiconductor Corporation

RRD-B30M75/Printed in U. S. A.

### **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage,  $V_{DD}-V_{SS}$  18V Allowable Input Voltage (Note 1)  $V_{SS}-0.3V$

Lead Temperature, V Pkg

Vapor Phase (60 sec)

+ 215°C

Infrared (15 sec)

+ 220°C

### **Operating Ratings**

$\begin{array}{lll} \text{Supply Voltage, V}_{DD} - \text{V}_{SS} & \text{5V to 16V} \\ \text{Digital Ground (Pin 13)} & \text{V}_{SS} \text{ to V}_{DD} \\ \text{Digital Input (Pins 14, 15, 16)} & \text{V}_{SS} \text{ to V}_{DD} \end{array}$

Analog Input (Pins 1, 2, 3, 4, 25, 26, 27)

(Note 1)  $V_{SS}$  to  $V_{DD}$ Operating Temperature,  $T_{opr}$   $-40^{\circ}$ C to  $+85^{\circ}$ C

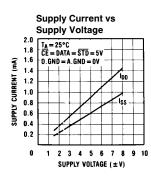

# **Electrical Characteristics** (Note 2) $V_{DD} = 7.5V$ , $V_{SS} = -7.5V$ , A.GND = 0V LOGIC SECTION

| Symbol              | Parameter                                                                      | Test Conditions                            | Тур   | Tested<br>Limit<br>(Note 3) | Design<br>Limit<br>(Note 4) | Unit<br>(Limit) |

|---------------------|--------------------------------------------------------------------------------|--------------------------------------------|-------|-----------------------------|-----------------------------|-----------------|

| I <sub>DDL</sub>    | Supply Current                                                                 | Pins 14, 15, 16 are 0V                     | 0.01  | 0.5                         | 0.5                         | mA (Max)        |

| I <sub>SSL</sub>    |                                                                                | Pins 14, 15, 16 are 0V                     | 0.01  | 0.5                         | 0.5                         | mA (Max)        |

| I <sub>DDH</sub>    |                                                                                | Pins 14, 15, 16 are 5V                     | 1.3   | 5                           | 5                           | mA (Max)        |

| Issh                |                                                                                | Pins 14, 15, 16 are 5V                     | 0.9   | 5                           | 5                           | mA (Max)        |

| V <sub>IH</sub>     | High-Level Input Voltage                                                       | @Pins 14, 15, 16                           | 1.8   | 2.3                         | 2.5                         | V (Min)         |

| V <sub>IL</sub>     | Low-Level Input Voltage                                                        | @Pins 14, 15, 16                           | 0.9   | 0.6                         | 0.4                         | V (Max)         |

| f <sub>o</sub>      | Clock Frequency                                                                | @Pin 14                                    | 2000  | 500                         | 500                         | kHz (Max)       |

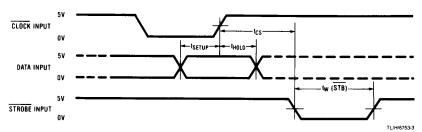

| t <sub>w(STB)</sub> | Width of STB Input                                                             | See Figure 1                               | 0.25  | 1                           | 1                           | μs (Min)        |

| t <sub>setup</sub>  | Data Setup Time                                                                | See Figure 1                               | 0.25  | 1                           | 1                           | μs (Min)        |

| t <sub>hold</sub>   | Data Hold Time                                                                 | See Figure 1                               | 0.25  | 1                           | 1                           | μs (Min)        |

| t <sub>cs</sub>     | Delay from Rising Edge of $\overline{\text{CLOCK}}$ to $\overline{\text{STB}}$ | See Figure 1                               | 0.25  | 1                           | 1                           | μs (Min)        |

| I <sub>IN</sub>     | Input Current                                                                  | @Pins 14, 15, 16 0V < V <sub>IN</sub> < 5V | ±0.01 | ±1                          |                             | μΑ (Max)        |

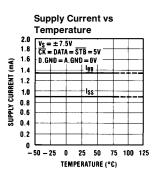

| C <sub>IN</sub>     | Input Capacitance                                                              | @Pins 14, 15, 16 f = 1 MHz                 | 5     |                             |                             | pF              |

Note 1: Pins 2, 3 and 26 have a maximum input voltage range of  $\pm 22V$  for the typical application shown in Figure 7.

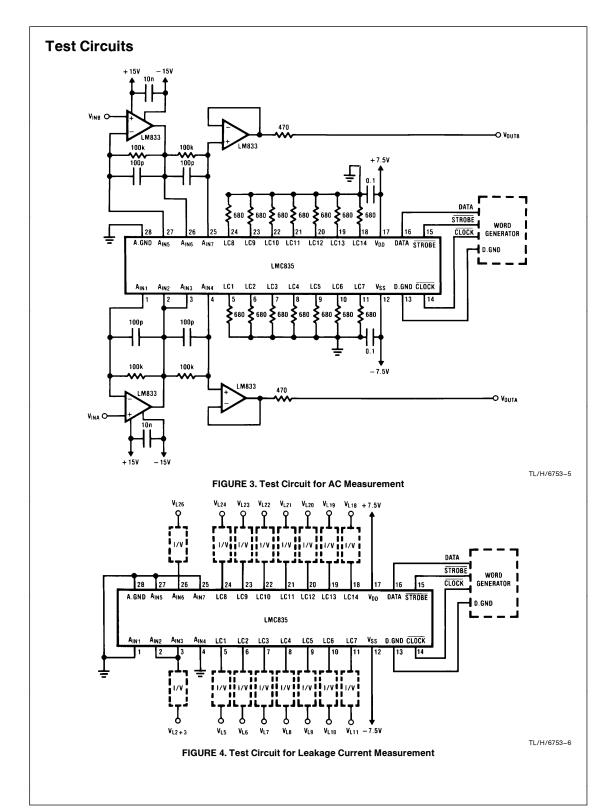

Note 2: Bold numbers apply at temperature extremes. All other numbers apply at T<sub>A</sub>=25°C, V<sub>DD</sub>=7.5V, V<sub>SS</sub>=-7.5V, D.GND=A.GND=0V as shown in the test circuit, Figures 3 and 4.

Note 3: Guaranteed and 100% production tested.

Note 4: Guaranteed (but not 100% production tested) over the operating temperature range. These limits are not used to calculate outgoing quality levels.

### **Timing Diagram**

TL/H/6753-3

Note: To change the gain of the presently selected band, it is not necessary to send DATA 1 (Band Selection) each time.

FIGURE 1

### **Electrical Characteristics** (Note 2) $V_{DD} = 7.5V$ , $V_{SS} = -7.5V$ , D.GND = A.GND = 0V

### SIGNAL PATH SECTION

| Symbol             | Parameter              | Test Conditions                                     | Тур    | Tested<br>Limit<br>(Note 3) | Design<br>Limit<br>(Note 4) | Unit<br>(Limit)        |

|--------------------|------------------------|-----------------------------------------------------|--------|-----------------------------|-----------------------------|------------------------|

| EA                 | Gain Error             | A <sub>V</sub> =0 dB @ ± 12 dB Range                | 0.1    | 0.5                         | 0.5                         | dB (Max)               |

| 1                  |                        | A <sub>V</sub> =0 dB @ ± 6 dB Range                 | 0.1    | 1                           | 1                           | dB (Max)               |

|                    |                        | A <sub>V</sub> = ±1 dB @ ± dB Range                 | 0.1    | 0.5                         | 0.6                         | dB (Max)               |

|                    |                        | (R <sub>5b</sub> or R <sub>5c</sub> is ON)          |        |                             |                             |                        |

|                    |                        | $A_V = \pm 2 \text{ dB } @ \pm 12 \text{ dB Range}$ | 0.1    | 0.5                         | 0.6                         | dB (Max)               |

|                    |                        | (R <sub>4b</sub> or R <sub>4c</sub> is ON)          |        |                             |                             |                        |

|                    |                        | $A_V = \pm 3 \text{ dB } @ \pm 12 \text{ dB Range}$ | 0.1    | 0.5                         | 0.6                         | dB (Max)               |

|                    |                        | (R <sub>3b</sub> or R <sub>3c</sub> is ON)          |        |                             |                             |                        |

|                    |                        | $A_V = \pm 4 \text{ dB } @ \pm 12 \text{ dB Range}$ | 0.1    | 0.5                         | 0.7                         | dB (Max)               |

|                    |                        | (R <sub>2b</sub> or R <sub>2c</sub> is ON)          |        |                             |                             |                        |

|                    |                        | A <sub>V</sub> = ±5 dB @ ± 12 dB Range              | 0.1    | 0.5                         | 0.7                         | dB (Max)               |

|                    |                        | (R <sub>1b</sub> or R <sub>1c</sub> is ON)          |        |                             |                             |                        |

|                    |                        | $A_V = \pm 9 \text{ dB } @ \pm 12 \text{ dB Range}$ | 0.2    | 1                           | 1.3                         | dB (Max)               |

|                    |                        | (R <sub>0b</sub> or R <sub>0c</sub> is ON)          |        |                             |                             |                        |

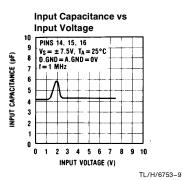

| THD                | Total Harmonic         | $A_V$ =0 dB @ $\pm$ 12 dB Range                     | 0.0015 |                             |                             | %                      |

|                    | Distortion             | $V_{IN} = 4V_{rms}$ , f = 1 kHz                     |        |                             |                             |                        |

|                    |                        | $A_V$ = 12 dB @ $\pm$ 12 dB Range                   |        |                             |                             |                        |

|                    |                        | $V_{IN} = 1V_{rms}$ , f = 1 kHz                     | 0.01   | 0.1                         |                             | % (Max)                |

|                    |                        | $V_{IN} = 1V_{rms}$ , f = 20 kHz                    | 0.1    | 0.5                         |                             | % (Max)                |

|                    |                        | $A_V = -12 \text{ dB } @ \pm 12 \text{ dB Range}$   |        |                             |                             |                        |

|                    |                        | $V_{IN} = 4V_{rms}$ , $f = 1 \text{ kHz}$           | 0.01   | 0.1                         |                             | % (Max)                |

|                    |                        | $V_{IN} = 4V_{rms}$ , f = 20 kHz                    | 0.1    | 0.5                         |                             | % (Max)                |

| V <sub>O Max</sub> | Maximum Output Voltage | $A_V$ =0 dB @ $\pm$ 12 dB Range                     | 5.5    | 5.1                         | 5                           | V <sub>rms</sub> (Min) |

|                    |                        | THD <1%, f=1 kHz                                    |        |                             |                             |                        |

| S/N                | Signal to Noise Ratio  | A <sub>V</sub> =0 dB @ ±12 dB Range                 | 114    |                             |                             | dB                     |

|                    |                        | V <sub>ref</sub> =1 V <sub>rms</sub>                |        |                             |                             |                        |

|                    |                        | A <sub>V</sub> = 12 dB @ ± 12 dB Range              | 106    |                             |                             | dB                     |

|                    |                        | $V_{ref} = 1V_{rms}$                                |        |                             |                             |                        |

|                    |                        | $A_V = -12 \text{ dB } @ \pm 12 \text{ dB Range}$   | 116    |                             |                             | dB                     |

|                    |                        | V <sub>ref</sub> =1V <sub>rms</sub>                 |        |                             |                             |                        |

| I <sub>LEAK</sub>  | Leakage Current        | A <sub>V</sub> =0 dB @ ±12 dB Range                 |        |                             |                             |                        |

| LLAN               |                        | (All internal switches are OFF)                     |        |                             |                             |                        |

|                    |                        | Pin 2+3, Pin 26                                     |        | 500                         |                             | nA (Max)               |

|                    |                        | Pin 5 ~ Pin 11, Pin 18 ~ Pin 24                     |        | 50                          |                             | nA (Max)               |

Note 2; Boldface numbers apply at temperature extremes. All other numbers apply at T<sub>A</sub>=25°C, V<sub>DD</sub>=7.5V, V<sub>SS</sub>=-7.5V, D.GND=A.GND=0V as shown in the test circuit, Figures 3 and 4.

Note 3: Guaranteed and 100% production tested.

Note 4: Guaranteed (but not 100% production tested) over the operating temperature range. These limits are not used to calculate outgoing quality levels.

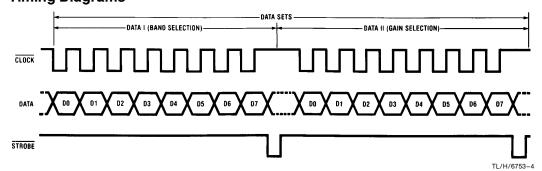

### **Timing Diagrams**

Note: To change the gain of the presently selected band, it is not necessary to send DATA 1 (Band Selection) each time.

FIGURE 2

### **Truth Tables**

**DATA I (Band Selection)**

| D7       | D6 | D5       | D4 | <b>D</b> 3         | D2       | D1      | D0            |

|----------|----|----------|----|--------------------|----------|---------|---------------|

| Н        | Х  | L        | L  | L                  | L        | L       | L             |

| Н        | Х  | L        | L  | L                  | L        | L       | Н             |

| Н        | Х  | L        | L  | L                  | L        | Н       | L             |

| Н        | Х  | L        | L  | L                  | L        | Н       | Н             |

| Н        | Х  | L        | L  | L                  | Н        | L       | L             |

| Н        | Х  | L        | L  | L                  | Н        | L       | Н             |

| Н        | Х  | L        | L  | L                  | Н        | Н       | L             |

| Н        | Х  | L        | L  | L                  | Н        | Н       | Н             |

| Н        | Х  | L        | L  | Н                  | L        | L       | L             |

| Н        | Х  | L        | L  | Н                  | L        | L       | Н             |

| Н        | Х  | L        | L  | Н                  | L        | Н       | L             |

| Н        | Х  | L        | L  | Н                  | L        | Н       | Н             |

| Н        | Х  | L        | L  | Н                  | Н        | L       | L             |

| Н        | Х  | L        | L  | Н                  | Н        | L       | Н             |

| Н        | Х  | L        | L  | Н                  | Н        | Н       | L             |

| Н        | Х  | L        | L  | Н                  | Н        | Н       | Н             |

| Н        | Х  | L        | Н  | V                  | alid Bin | ary Inp | ut            |

| Н        | Х  | Н        | L  | V                  | alid Bin | ary Inp | ut            |

| Н        | Х  | Н        | Н  | Valid Binary Input |          |         | ut            |

| <b>↑</b> | 1  | <b>1</b> | 1  | ←                  | Band     | Code    | $\rightarrow$ |

| ①        | 2  | 3        | 4  |                    |          |         |               |

(Ch A: Band  $1 \sim 7$ , Ch B: Band  $8 \sim 14$ )

Ch A  $\pm$  12 dB Range, Ch B  $\pm$  12 dB Range, No Band Selection Ch A  $\pm$  12 dB Range, Ch B  $\pm$  12 dB Range, Band 1

Ch A  $\pm$  12 dB Range, Ch B  $\pm$  12 dB Range, Band 2 Ch A  $\pm$  12 dB Range, Ch B  $\pm$  12 dB Range, Band 3

Ch A  $\pm$  12 dB Range, Ch B  $\pm$  12 dB Range, Band 4

Ch A  $\pm$  12 dB Range, Ch B  $\pm$  12 dB Range, Band 5

Ch A  $\pm$  12 dB Range, Ch B  $\pm$  12 dB Range, Band 6

Ch A  $\pm$  12 dB Range, Ch B  $\pm$  12 dB Range, Band 7

Ch A  $\pm$  12 dB Range, Ch B  $\pm$  12 dB Range, Band 8 Ch A  $\pm$  12 dB Range, Ch B  $\pm$  12 dB Range, Band 9

Ch A  $\pm$  12 dB Range, Ch B  $\pm$  12 dB Range, Band 10

Ch A  $\pm$  12 dB Range, Ch B  $\pm$  12 dB Range, Band 11

Ch A  $\pm$  12 dB Range, Ch B  $\pm$  12 dB Range, Band 12

Ch A  $\pm$  12 dB Range, Ch B  $\pm$  12 dB Range, Band 13

Ch A  $\pm$  12 dB Range, Ch B  $\pm$  12 dB Range, Band 14 Ch A  $\pm$  12 dB Range, Ch B  $\pm$  12 dB Range, No Band Selection

Ch A  $\pm$  12 dB Range, Ch B  $\pm$  6 dB Range, Band 1  $\sim$  14

Ch A  $\pm$  6 dB Range, Ch B  $\pm$  12 dB Range, Band 1  $\sim$  14

Ch A  $\pm$  6 dB Range, Ch B  $\pm$  6 dB Range, Band 1  $\sim$  14

- ① DATA 1

- @ Don't Care

- $\bullet$  Ch B  $\pm 6$  dB/ $\pm 12$  dB Range

### **DATA II (Gain Selection)**

D7 D6 D5 D4 D3 D2 D1 D0 Flat L Х L L L L L L 1 dB Boost L Н Н L L L L L 2 dB Boost L Н L Н L L L L 3 dB Boost L Н L L Н L L L 4 dB Boost L Н L L L Н L L 5 dB Boost Н Н L L L L L L 6 dB Boost L Н L Н L Н L 7 dB Boost L Н Н L Н L Н L 8 dB Boost L Н L Н L Н Н L 9 dB Boost L Н L L L L L Н 10 dB Boost L Н Н Н L Н L L 11 dB Boost L Н Н Н Н Н 12 dB Boost L Н Н Н 1 dB  $\sim$  12 dB Cut L L Valid Above Input 1 1 Gain Code → (5) 6

- This is the gain if the  $\,\pm\,12$  dB range is selected by DATA I. If the  $\pm 6~\mathrm{dB}$ range is selected, then the values shown must be approximately halved. See the characteristics curves for more exact data.

- ⑤ DATA II

- Boost/Cut

# Test Circuits (Continued)

V<sub>LOUT</sub> = |<sub>UN</sub> × 10<sup>7</sup>

FIGURE 5. I to V Converter

TL/H/6753-7

FIGURE 6. Simple Word Generator

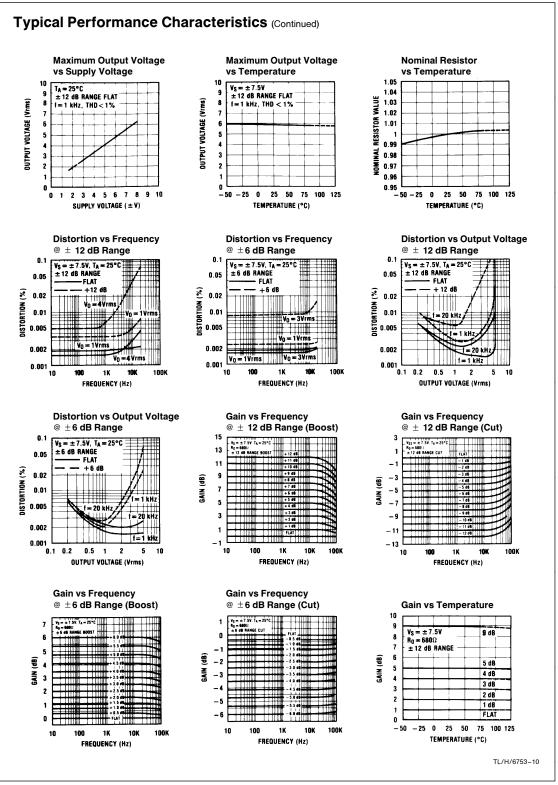

### **Typical Performance Characteristics**

#

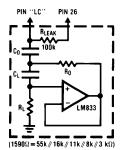

FIGURE 7. Stereo 7-Band Equalizer

**TABLE I: Tuned Circuit Elements**

+ 15V

| Q <sub>0</sub> =3.5, Q <sub>12dB</sub> =1.05 |                     |                    |                    |               |                           |  |  |

|----------------------------------------------|---------------------|--------------------|--------------------|---------------|---------------------------|--|--|

| <b>Z</b> 1                                   | f <sub>o</sub> (Hz) | C <sub>O</sub> (F) | C <sub>L</sub> (F) | $R_L(\Omega)$ | <b>R</b> <sub>O</sub> (Ω) |  |  |

| Z1                                           | 63                  | 1μ                 | 0.1μ               | 100k          | 680                       |  |  |

| Z2                                           | 160                 | $0.47\mu$          | 0.033μ             | 100k          | 680                       |  |  |

| Z3                                           | 400                 | $0.15 \mu$         | 0.015μ             | 100k          | 680                       |  |  |

| Z4                                           | 1k                  | $0.068 \mu$        | $0.0068 \mu$       | 82k           | 680                       |  |  |

| Z5                                           | 2.5k                | $0.022 \mu$        | 0.0033μ            | 82k           | 680                       |  |  |

| Z6                                           | 6.3k                | $0.01\mu$          | 0.0015μ            | 62k           | 680                       |  |  |

| Z7                                           | 16k                 | $0.0047\mu$        | 680p               | 47k           | 680                       |  |  |

TL/H/6753-11

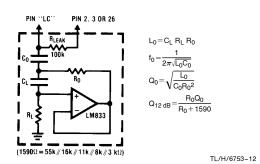

FIGURE 8. Tuned Circuit for Stereo 7-Band Equalizer (Figure 7)

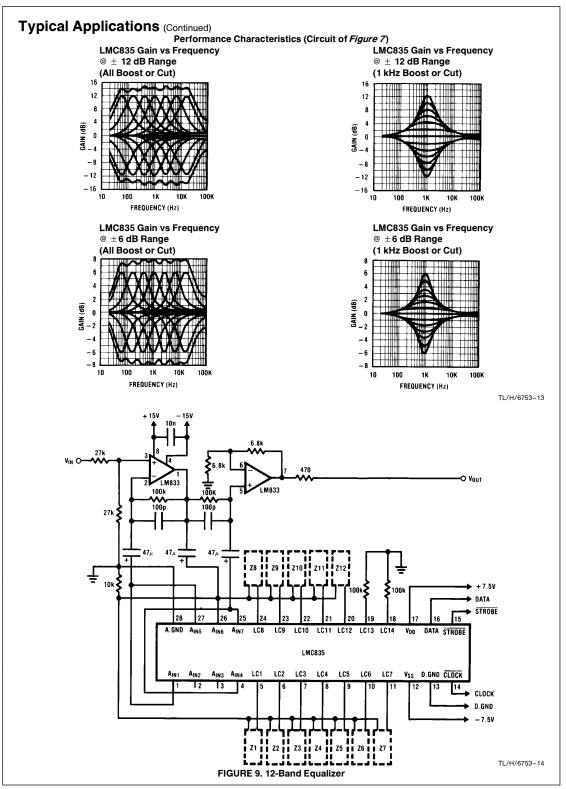

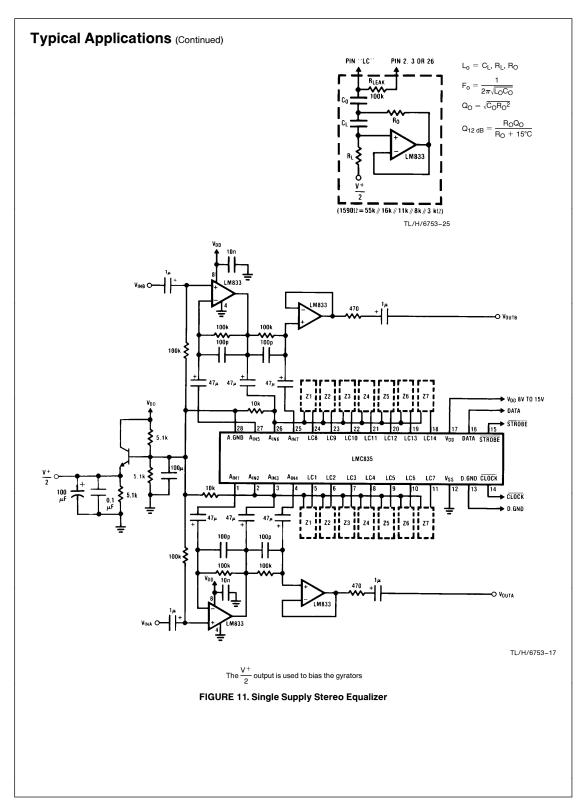

### Typical Applications (Continued)

**TABLE II. Tuned Circuit Elements**

| Q <sub>0</sub> =4.7, Q <sub>12 dB</sub> =1.4 |                     |                    |                    |               |               |  |  |

|----------------------------------------------|---------------------|--------------------|--------------------|---------------|---------------|--|--|

|                                              | f <sub>o</sub> (Hz) | C <sub>o</sub> (F) | C <sub>L</sub> (F) | $R_L(\Omega)$ | $R_o(\Omega)$ |  |  |

| Z1                                           | 16                  | 3.3µ               | 0.47μ              | 100k          | 680           |  |  |

| Z2                                           | 31.5                | 15μ                | 0.22μ              | 110k          | 680           |  |  |

| Z3                                           | 63                  | 1μ                 | 0.1μ               | 100k          | 680           |  |  |

| Z4                                           | 125                 | $0.39 \mu$         | 0.068μ             | 91k           | 680           |  |  |

| Z5                                           | 250                 | 0.22μ              | 0.033μ             | 82k           | 680           |  |  |

| Z6                                           | 500                 | 0.1μ               | 0.015μ             | 100k          | 680           |  |  |

| Z7                                           | 1k                  | 0.047μ             | 0.01μ              | 82k           | 680           |  |  |

| Z8                                           | 2k                  | 0.022μ             | 0.0047μ            | 91k           | 680           |  |  |

| Z9                                           | 4k                  | 0.01μ              | 0.0022μ            | 110k          | 680           |  |  |

| Z10                                          | 8k                  | $0.0068 \mu$       | 0.001μ             | 82k           | 680           |  |  |

| Z11                                          | 16k                 | $0.0033 \mu$       | 680p               | 62k           | 680           |  |  |

| Z12                                          | 32k                 | $0.0015\mu$        | 470p               | 68k           | 510           |  |  |

TL/H/6753-15

FIGURE 10. Tuned Circuit for 12-Band Equalizer (Figure 9)

### Performance Characteristics (Circuit of Figure 9)

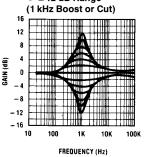

12 Band Equalizer Application LMC835 Gain vs Frequency

# 12 Band Equalizer Application LMC835 Gain vs Frequency

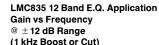

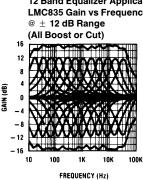

### LMC835 12 Band E.Q. Application

TL/H/6753-16

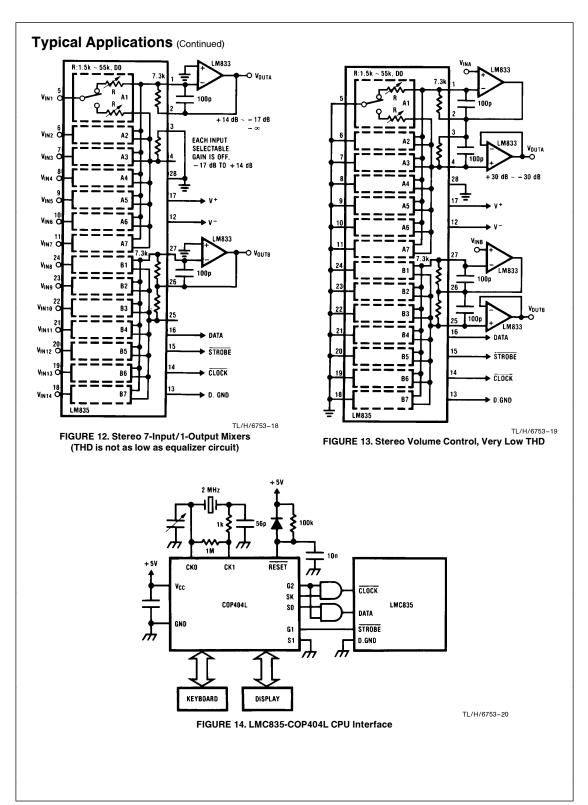

### Typical Applications (Continued)

### Sample Subroutine Program for Figure 14, LMC835-COP404L CPU Interface

| HEX  |         |         |           |                                               |

|------|---------|---------|-----------|-----------------------------------------------|

| CODE | LABEL   | MNEMONI | cs        | COMMENTS                                      |

| 3F   | LMC835: | LBI     | 3F        | ;POINT TO RAMADDRESS 3F                       |

| 05   | SEND    | LD      |           | ;RAMDATA TO A                                 |

| 22   |         | SC      |           | ; SET CARRY                                   |

| 335F |         | OGI     |           | ;SET PORT G= 1111, OPEN THE AND GATES         |

| 4F   |         | XAS     |           | ;SWAP A AND SIO, CLOCK START                  |

| 05   |         | LD      |           | ;RAMDATA TO A, MAKE SURE A = DATA             |

| 07   |         | XDS     |           | ;SWAP A AND RAMDATA, RAMADDRESS=RAMADDRESS-1  |

| 05   |         | LD      |           | ;RAMDATA TO A                                 |

| 4F   |         | XAS     |           | ;SWAP A AND SIO                               |

| 05   |         | LD      |           | ;RAMDATA TO A, MAKE SURE A=NEWDATA            |

| 07   |         | XDS     |           | ;SWAP A AND RAMDATA, RAMADDRESS=RAMADDRESS-1  |

| 32   |         | RC      |           | ;RESET CARRY                                  |

| 4F   |         | XAS     |           | ;SWAP A AND SIO, CLOCK STOP                   |

| 335D |         | OGJ     | 13        | ;SET PORT G=1101, MAKE STROBE LOW             |

| 335B |         | OGI     | 11        | ;SET PORT G=1011, MAKE STROBE HIGH, CLOSE THE |

|      |         |         |           | GATES                                         |

| 4E   |         | CBA     |           | ;BD TO A                                      |

| 43   |         | AISC    | 3         | ;RAMADDRESS < 3C THEN RETURN                  |

| 48   |         | RET     |           |                                               |

| 80   |         | JP      | SEND      |                                               |

|      |         |         |           |                                               |

|      | RAM     |         |           |                                               |

| A    | DDRESS  | COM     | MENTS     |                                               |

| 3C   | DATA    | ;GAIN D | ATA D4-D7 |                                               |

| 3D   | DATA    | ;GAIN D | ATA DO-D3 |                                               |

| 3E   | DATA    | ;BAND D | ATA D4-D7 |                                               |

| 3F   | DATA    | ;BAND D | ATA DO-D3 |                                               |

### **Application Hints**

### **SWITCHING NOISE**

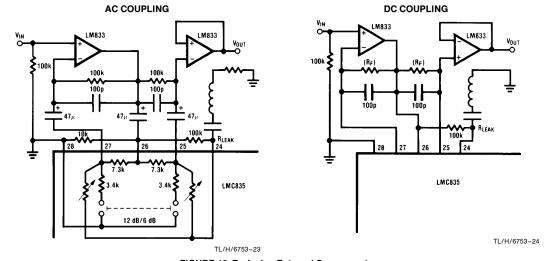

The LMC835 uses CMOS analog switches that have small leakages (less than 50 nA). When a band is selected for flat gain, all the switches in that band are open and the resonator circuit is not connected to the LMC835 resistor network. It is only in the flat mode that the small leakage currents can cause problems. The input to the resonator circuit is usually a capacitor and the leakage currents will slowly charge up this capacitor to a large voltage if there is no resistive path to limit it. When the band is set to any value other than flat, the charge on the capacitor will be discharged by the resistor network and there will be a transient at the output. To limit the size of this transient, R<sub>LEAK</sub> is necessary.

## HOW TO AVOID SWITCHING NOISE DUE TO LEAKAGE CURRENT (Refer to Figures 7 and $\theta$ )

To avoid switching noise due to leakage currents when changing the gain, it is recommended to put  $R_{LEAK}=100~\rm k\Omega$  between Pin 3 and Pin 5—11 each, Pin 26 and Pin 12—24 each. The resistor limits the voltage that the capacitor can charge to, with minimal effects on the equalization. The frequency response change due to  $R_{LEAK}$  are shown in Figure 15. The gain error is only 0.2 dB and Q error is only 5% at 12 dB boost or cut.

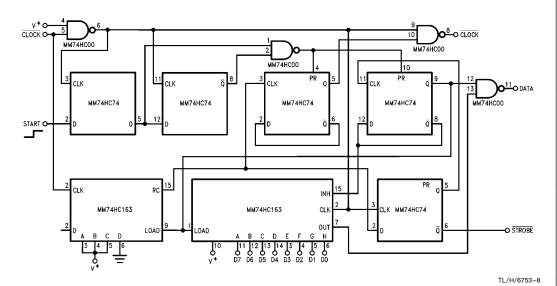

### **SIMPLE WORD GENERATOR** (Figure 6)

Circuit operation revolves around an MM74HC165 parallel-in/serial-out shift register. Data bits D0 through D7 are applied to the parallel of the MM74HC165 from 8 toggle switches. The bits are shifted out to the DATA input of the LMC835 in sync with the clock. When all data bits have been loaded, CLOCK is inhibited and a STROBE pulse is generated: this sequence is initiated by a START pulse.

### LMC835-COP404L CPU INTERFACE (Refer to Figure 14)

The diagram shows AND gates between the COP and the LMC835. These permit G2 to inhibit the CLOCK and DATA lines (SK and SO) during a STROBE (G1) pulse. This function may also be implemented in software. As shown in Figure 2, the data groups are shifted in D0 first. Data is loaded on positive clock edges.

### POWER SUPPLIES

These applications show LM317/337 regulators for the  $\pm$ 7.5V supplies for the LMC835. Since the latter draws only 5 mA max., 1k series dropping resistors from the  $\pm$ 15V op amp supply and a pair of 7.5V zeners and bypass caps will also suffice.

# Application Hints (Continued) MODEL IM 100k 12 dB 11.8 dB

FIGURE 15. Effect of R<sub>LEAK</sub>

TL/H/6753-21

### REDUCING EXTERNAL COMPONENTS

The typical application shown in Figure 7 is switching noise free. The DC-coupled circuit in Figure 16 is also switching noise free, except at 12 dB/6 dB switch turn ON/OFF. This switching noise is caused by the  $I_{\mbox{\scriptsize bias}}$  and  $V_{\mbox{\scriptsize offset}}$  of the op

amps. Selecting a low  $I_{bias}$  and  $V_{offset}$  op amp can minimize the switching noise due to the 12 dB/6 dB switch. The DC-coupled application can also eliminate the  $R_F$ = 100k resistors with only a 0.5 dB gain error at 12 dB boost or cut.

TL/H/6753-22

*ω*<sub>0</sub>/10

FIGURE 16. Reducing External Components

### Physical Dimensions inches (millimeters) (Continued)

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 2900 Semiconductor Drive P.O. Box 58090 Santa Clara, CA 95052-8090 Tel: 1(800) 272-9959 TWX: (910) 339-9240 National Semiconductor GmbH Livry-Gargan-Str. 10 D-82256 Fürstenfeldbruck Germany Tel: (81-41) 35-0 Telex: 527649 Fax: (81-41) 35-1 National Semiconductor Japan Ltd. Sumitomo Chemical Engineering Center Bldg. 7F 1-7-1, Nakase, Mihama-Ku Chiba-City, Ciba Prefecture 261

Mational Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon U Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960 National Semiconductores Do Brazil Ltda. Rue Deputado Lacorda Franco 120-3A Sao Paulo-SP Brazil 05418-000 Tel: (55-11) 212-5066 Telex: 391-1131931 NSBR BR Fax: (55-11) 212-1181 National Semiconductor (Australia) Pty, Ltd. Building 16 Business Park Drive Monash Business Park Nottinghill, Melbourne Victoria 3168 Australia Tel: (3) 558-9999 Fax: (3) 558-9998