-

Componentes Electrónicos

- Antenas

- Borneras

- Borneras Enchufables

- Cables

- Calentamiento/Enfriamiento

- Capacitores

- CI Lógicos CMOS/TTL

- CI Reguladores de Tensión

- Circuitos Integrados

- Conectores

- Cristales y Resonadores

- Diodos

- Displays

- Fotodiodos

- Fototransistores

- Gabinetes

- IGBT

- Impresoras Termicas

- Interruptores

- LED

- Microcontroladores

- Módulos "GPS" (GNSS)

- Módulos de Comunicación

- Módulos SOM/SBC

- Optoacopladores

- PolySwitchs

- Precintos y Separadores

- Protoboards/Placas

- Reed Switches

- Reles

- Resistencias Variables

- Sensores

- Tiristores

- Transistores

- Triacs

- Varistores

-

Instrumental & Medición

- Accesorios

- Analizadores Calidad de Energía

- Analizadores de Espectro

- Anemómetros

- Boroscopios

- Cámaras Termográficas

- Combo Instrumental

- Decibelímetro

- Detectores de tensión

- Frecuencímetros de Banco

- Fuentes de Laboratorio

- Generadores de Funciones

- Luxómetro

- Medidor de distancia laser

- Medidores Ambientales

- Medidores de Fibra Óptica

- Medidores de Potencia

- Medidores de Vibraciónes

- Medidores LCR

- Megóhmetros

- Miliohmetros

- Milivoltímetros de Banco

- Multímetros

- Nivel Laser

- Osciloscopios

- Pinzas Amperométricas

- Probadores de Cables/Red

- Probadores de disyuntores

- Puntas Lógicas

- Secuencímetros

- Tacómetros

- Telurímetros

- Termohigrómetros

- Termómetros

- Varios

- Arduino

- Raspberry

- Desarrollo

- Herramientas

- Energía Solar

- E-SHOP

.jpg)

Ahorre

12

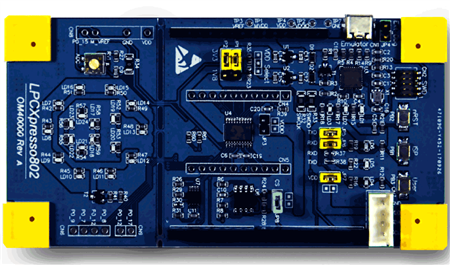

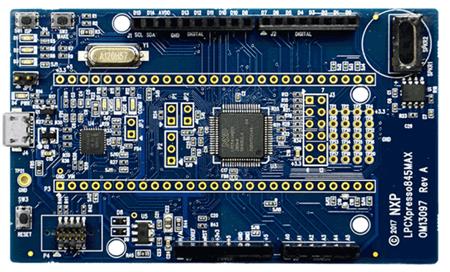

Placa de Desarrollo Lpcxpresso Lpcxpresso1769cd Arm Cortex M3

LPC1769XPS.RV.D

Pagá hasta en 12 Cuotas

Calculá tus Cuotas

- Retiro en Sucursal: GRATIS!

- Retiro en Sucursal de Correo

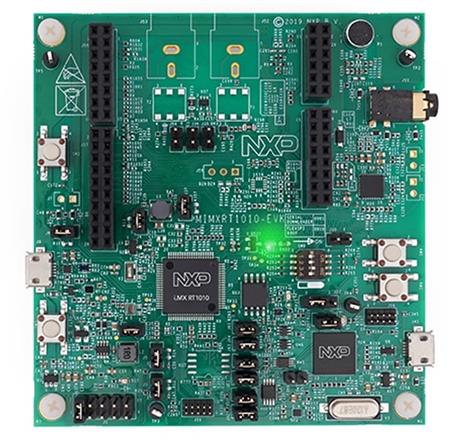

Marca: NXP

LPC1769 es unpla con microcontrolador Cortex®-M3 para aplicaciones integradas que ofrece un alto nivel de integración y bajo consumo de energía en frecuencias de 120 MHz.El LPC1769 es compatible con los pines del MCU LPC2368 Arm7 ™ de 100 pines.

La tarjeta LPCXpresso1769 con CMSIS-DAP que contiene el microcontrolador

ARM Cortex-M3 de NXP ha sido diseñada para que sea lo más sencillo comenzar

a trabajar con microprocesadores Cortex-M3.

Código: LPC1769XPS.RV.D

Descripción

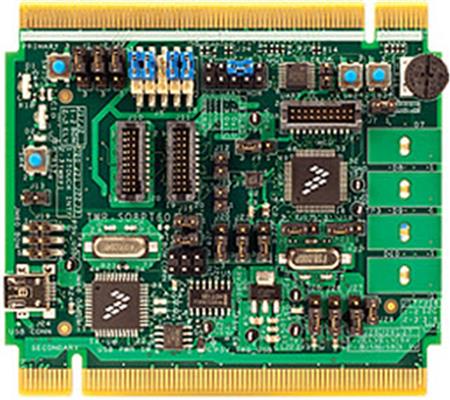

Esta versión actualizada tiene varias mejoras;

La interfaz de debugg es compatible con CMSIS-DAP, lo que significa

que es compatible con muchos entornos de desarrollo,

incluyendo (pero no limitado a) LPCXpresso IDE,

uVision de Keil / ARM, Embedded Workbench de IAR, etc.

El debugger CMSIS-DAP se puede deshabilitar con un puente,

lo que permite conectar un debugger externo (a través de un conector

de debug Cortex estándar de 10 pos)

El lado de debugg se puede quitar de una manera más sencilla que antes

(snap / break off), pero tenga en cuenta que no es posible reconectar las

dos partes de nuevo.

Después de romper el lado de debug, recomendamos

usar LPC-Link2 como la solución de debug.

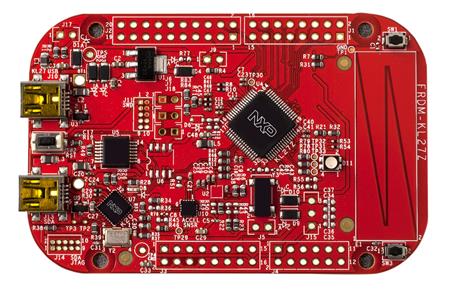

Se ha añadido RGB-LED

Se ha añadido el pulsador ISP-enable

Se ha agregado el pulsador de reinicio

La PCB es un diseño de 4 capas con una mejor conexión a tierra y

diseño de la fuente de alimentación, lo que hace que la placa sea

más adecuada para la integración

Caracteristicas

- Procesador Arm® Cortex-M3

- Controlador de interrupciones de vector anidado integrado (NVIC) de Arm Cortex-M3

- Memoria de programación flash en chip de hasta 512 kB

- SRAM en chip de hasta 64 kB

- Programación en el sistema (ISP) y Programación en la aplicación (IAP)

- Controlador DMA de propósito general de ocho canales (GPDMA)

- Ethernet MAC con interfaz RMII y controlador DMA dedicado

- Dispositivo USB 2.0 de velocidad completa / Host / controlador OTG

- Cuatro UART con generación de velocidad en baudios fraccional, FIFO interno y soporte DMA

- Controlador CAN 2.0B con dos canales.

- Controlador SPI con comunicación síncrona, serial, dúplex completo

- Dos controladores SSP con FIFO y capacidades multiprotocolo.

- Tres interfaces de bus I2C mejoradas

- Interfaz I2S (Inter-IC Sound)

- 70 pines de E / S de propósito general (GPIO)

- Convertidor analógico/digital (ADC) de 12 bits / 8 canales

- Convertidor digital / analógico (DAC) de 10 bits con temporizador de conversión dedicado y DMA

- Cuatro contadores de propósito general

- Un control de motor PWM con soporte para control de motor trifásico

- Interfaz del codificador de cuadratura que puede monitorear un codificador de cuadratura externo

- Un bloque de temporizador / PWM estándar con entrada de conteo externa

- RTC de baja potencia con un dominio de potencia separado y un oscilador dedicado

Temporizador de vigilancia (WDT)

-Temporizador de interrupción repetitiva proporciona interrupciones programadas y repetidas temporizadas

- PMU integrada (Unidad de administración de energía)

- Cuatro modos de potencia reducida: reposo, apagado profundo, apagado y apagado profundo

- Entrada de interrupción no enmascarable (NMI)

- Controlador de interrupción de activación (WIC)

- Activación del procesador desde el modo de apagado a través de cualquier interrupción

- Detección de interrupciones parciales con umbral separado para interrupción y reinicio forzado

- Reinicio de encendido (POR)

Ficha técnica

| Marcas: | NXP |

.jpg)

.jpg)

.png)

.jpg)